पुढे, आम्ही उच्च गुणोत्तर HDI बोर्डांच्या इलेक्ट्रोप्लेटिंग क्षमतांचा अभ्यास करणे सुरू ठेवतो.

I. उत्पादन माहिती:

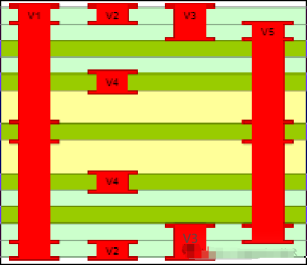

- बोर्डची जाडी: 2.6 मिमी, किमान थ्रू-होल व्यास: 0.25 मिमी,

- कमाल थ्रू-होल आस्पेक्ट रेशो: 10.4:1;

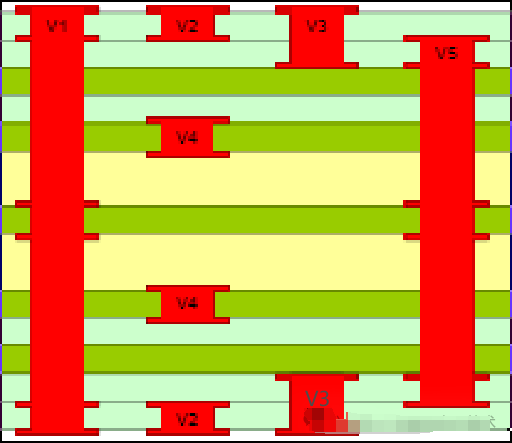

II. अंध मार्ग:

- 1) डायलेक्ट्रिक जाडी: 70um (1080pp), छिद्र व्यास: 0.1 मिमी

- 2) डायलेक्ट्रिक जाडी: 140um (2*1080pp), छिद्र व्यास: 0.2mm

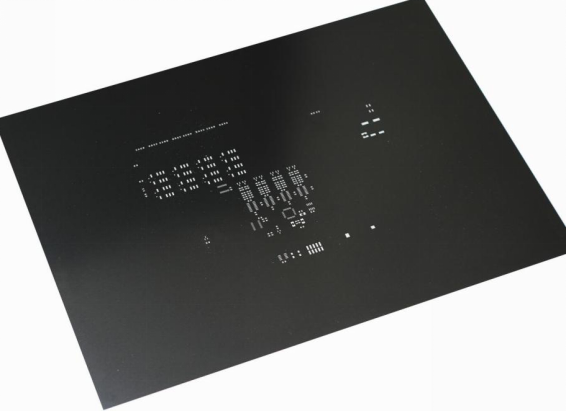

III. पॅरामीटर सेटिंग स्कीम:

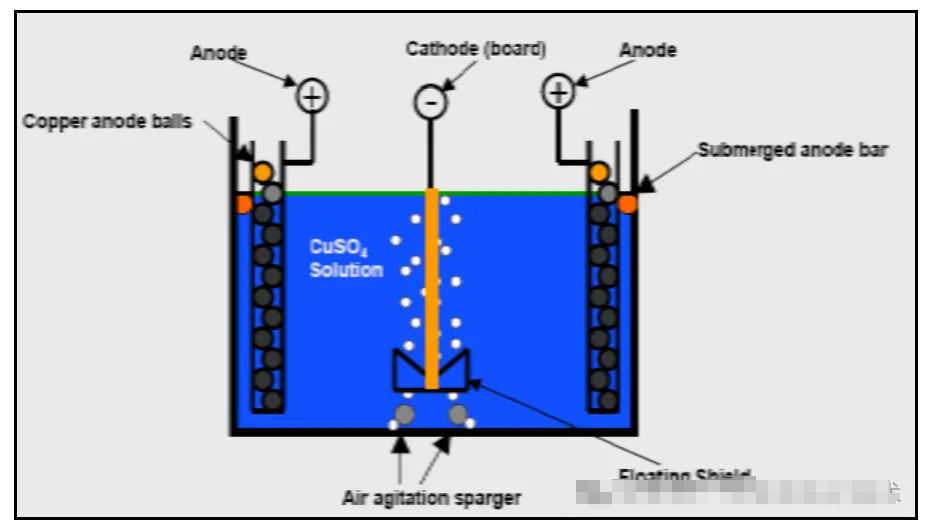

योजना एक: कॉपर प्लेटिंग नंतर डायरेक्ट इलेक्ट्रोप्लेटिंग

- एच इलेक्ट्रोप्लेटिंग ऍडिटीव्हसह, उच्च ऍसिड लो कॉपर सोल्यूशन गुणोत्तर वापरणे; वर्तमान घनता 10ASF, इलेक्ट्रोप्लेटिंग वेळ 180min.

-- अंतिम सातत्य चाचणी परिणाम

उत्पादनांच्या या बॅचमध्ये अंतिम सातत्य चाचणीमध्ये 100% ओपन सर्किट दोष दर होता, 70% ओपन सर्किट दोष दर 0.2 मिमी ब्लाइंड द्वारे स्थानावर होता (PP 1080*2 आहे).

योजना दोन: पारंपारिक इलेक्ट्रोप्लेटिंग सोल्यूशन वापरून ब्लाइंड व्हियास थ्रू-होल प्लेटिंग करण्यापूर्वी:

1) पारंपारिक ऍसिड कॉपर रेशो आणि H इलेक्ट्रोप्लेटिंग ॲडिटीव्हसह, ब्लाइंड वायस प्लेट करण्यासाठी VCP वापरणे, इलेक्ट्रोप्लेटिंग पॅरामीटर्स 15ASF, इलेक्ट्रोप्लेटिंग वेळ 30 मिनिटे {190} {190} {190}

2) उच्च ऍसिड लो कॉपर रेशो आणि एच इलेक्ट्रोप्लेटिंग ॲडिटीव्हसह, घट्ट करण्यासाठी गॅन्ट्री लाइन वापरणे, इलेक्ट्रोप्लेटिंग पॅरामीटर्स 10ASF, इलेक्ट्रोप्लेटिंग वेळ 150 मिनिटे {4906281} {49062810}

-- अंतिम सातत्य चाचणी परिणाम उत्पादनांच्या या बॅचमध्ये अंतिम सातत्य चाचणीमध्ये 45% ओपन सर्किट दोष दर होता, 60% ओपन सर्किट दोष दर 0.2 मिमी आंधळे स्थानाद्वारे (PP 1080*2 आहे) {४९०९१०१} {४९०९१०१} {६०८२०९७}

दोन प्रयोगांची तुलना करताना, मुख्य समस्या ब्लाइंड वायसच्या इलेक्ट्रोप्लेटिंगची होती, ज्याने हे देखील पुष्टी केली की उच्च ऍसिड लो कॉपर सोल्यूशन सिस्टम अंध वियाससाठी योग्य नाही. म्हणून, तीन प्रयोगात, ब्लाइंड व्हियासला प्रथम प्लेट करण्यासाठी कमी आम्लयुक्त उच्च तांबे भरण्याचे द्रावण निवडले गेले, आंधळ्या विअसला इलेक्ट्रोप्लेटिंग करण्यापूर्वी ब्लाइंड व्हियाच्या तळाशी घट्ट भरले. स्कीम तीन: थ्रू-होल प्लेटिंग करण्यापूर्वी ब्लाइंड व्हियास प्लेट करण्यासाठी फिलिंग इलेक्ट्रोप्लेटिंग सोल्यूशन वापरणे: 1) ब्लाइंड वायस प्लेट करण्यासाठी फिलिंग इलेक्ट्रोप्लेटिंग सोल्यूशन वापरणे, उच्च कॉपर लो ऍसिड ऍसिड कॉपर रेशो आणि व्ही इलेक्ट्रोप्लेटिंग ॲडिटीव्हसह, इलेक्ट्रोप्लेटिंग पॅरामीटर्स 8ASF@30min + 12ASF@30min {0919} {049} } {६०८२०९७}

2) उच्च ऍसिड लो कॉपर रेशो आणि एच इलेक्ट्रोप्लेटिंग ॲडिटीव्हसह, घट्ट करण्यासाठी गॅन्ट्री लाइन वापरणे, इलेक्ट्रोप्लेटिंग पॅरामीटर्स 10ASF, इलेक्ट्रोप्लेटिंग वेळ 150 मिनिटे {4906281} {49062810}

IV. प्रायोगिक डिझाइन आणि परिणाम विश्लेषण प्रायोगिक तुलनेद्वारे, भिन्न आम्ल तांबे गुणोत्तर आणि इलेक्ट्रोप्लेटिंग ऍडिटीव्ह्सचा थ्रू आणि ब्लाइंड होलवर भिन्न इलेक्ट्रोप्लेटिंग प्रभाव असतो. थ्रू आणि ब्लाइंड होल अशा उच्च आस्पेक्ट रेशो असलेल्या HDI बोर्डसाठी, थ्रू होलच्या आतील तांब्याची जाडी आणि आंधळ्या छिद्रांच्या क्रॅब्स फूट इश्यूशी सुसंगत संतुलन बिंदू आवश्यक आहे. अशाप्रकारे प्रक्रिया केलेल्या पृष्ठभागावरील तांब्याची जाडी साधारणपणे जाड असते आणि बाह्य स्तर कोरीव कामासाठी प्रक्रिया आवश्यकता पूर्ण करण्यासाठी यांत्रिक ब्रशिंग वापरणे आवश्यक असू शकते. चाचणी उत्पादनांच्या पहिल्या आणि दुस-या बॅचमध्ये अंतिम कॉपर ब्रेक चाचणीमध्ये अनुक्रमे 100% आणि 45% ओपन सर्किट दोष होते, विशेषत: 0.2 मिमी अंध असलेल्या ठिकाणी (PP 1080*2) ओपन सर्किट दोष दर अनुक्रमे 70% आणि 60% आहेत, तर तिसऱ्या बॅचमध्ये हा दोष नव्हता आणि प्रभावी सुधारणा दर्शवून 100% उत्तीर्ण झाले. ही सुधारणा उच्च गुणोत्तर एचडीआय बोर्डच्या इलेक्ट्रोप्लेटिंग प्रक्रियेसाठी एक प्रभावी उपाय प्रदान करते, परंतु पृष्ठभागाची पातळ तांबे जाडी प्राप्त करण्यासाठी पॅरामीटर्सना अद्याप अनुकूल करणे आवश्यक आहे. वरील सर्व, उच्च गुणोत्तर HDI बोर्डांच्या इलेक्ट्रोप्लेटिंग क्षमतांचा अभ्यास करण्यासाठी विशिष्ट प्रायोगिक योजना आणि परिणाम आहेत.

मराठी

मराठी English

English Español

Español Português

Português русский

русский français

français 日本語

日本語 Deutsch

Deutsch Tiếng Việt

Tiếng Việt Italiano

Italiano Nederlands

Nederlands ไทย

ไทย Polski

Polski 한국어

한국어 Svenska

Svenska magyar

magyar Malay

Malay বাংলা

বাংলা Dansk

Dansk Suomi

Suomi हिन्दी

हिन्दी Pilipino

Pilipino Türk

Türk Gaeilge

Gaeilge عربى

عربى Indonesia

Indonesia norsk

norsk اردو

اردو čeština

čeština Ελληνικά

Ελληνικά Українська

Українська Javanese

Javanese فارسی

فارسی தமிழ்

தமிழ் తెలుగు

తెలుగు नेपाली

नेपाली Burmese

Burmese български

български ລາວ

ລາວ Latine

Latine Қазақ

Қазақ Euskal

Euskal Azərbaycan

Azərbaycan slovenský

slovenský Македонски

Македонски Lietuvos

Lietuvos Eesti Keel

Eesti Keel Română

Română Slovenski

Slovenski Српски

Српски 简体中文

简体中文 Esperanto

Esperanto Afrikaans

Afrikaans Català

Català עִברִית

עִברִית Cymraeg

Cymraeg Galego

Galego 繁体中文

繁体中文 Latvietis

Latvietis icelandic

icelandic יידיש

יידיש Беларус

Беларус Hrvatski

Hrvatski Kreyòl ayisyen

Kreyòl ayisyen Shqiptar

Shqiptar Malti

Malti lugha ya Kiswahili

lugha ya Kiswahili አማርኛ

አማርኛ Bosanski

Bosanski Frysk

Frysk ជនជាតិខ្មែរ

ជនជាតិខ្មែរ ქართული

ქართული ગુજરાતી

ગુજરાતી Hausa

Hausa Кыргыз тили

Кыргыз тили ಕನ್ನಡ

ಕನ್ನಡ Corsa

Corsa Kurdî

Kurdî മലയാളം

മലയാളം Maori

Maori Монгол хэл

Монгол хэл Hmong

Hmong IsiXhosa

IsiXhosa Zulu

Zulu Punjabi

Punjabi پښتو

پښتو Chichewa

Chichewa Samoa

Samoa Sesotho

Sesotho සිංහල

සිංහල Gàidhlig

Gàidhlig Cebuano

Cebuano Somali

Somali Точик

Точик O'zbek

O'zbek Hawaiian

Hawaiian سنڌي

سنڌي Shinra

Shinra հայերեն

հայերեն Igbo

Igbo Sundanese

Sundanese Lëtzebuergesch

Lëtzebuergesch Malagasy

Malagasy Yoruba

Yoruba